•

復習コーナー

トランジスタの入出力インピーダンス

エミッタ接地のトランジスタにおいて

•

入力インピーダンスはhieである。

•

hieは10kW 程度である。

•

出力インピーダンスは1/hoeである。

•

hoeは1mS 程度である。出力インピーダンスは1M W 程度である。

増幅回路の入力インピーダンス

•

信号源からみて、増幅回路の入力端がもつ見かけのインピーダンスを入力インピーダンスという。

•

等価回路で考える。バイアス抵抗、トランジスタのhieが並列に接続されたと考えればよい。

•

Zin=1/(1/R1+1/hie)=R1hie/(R1+hie)

•

上では交流に対してコンデンサのインピーダンスは0であるとして扱ったが、正しくは、Z=1/jωCが直列につながっていると考えるべきである。

•

Zin=1/jwC+ R1hie/(R1+hie)

増幅回路の出力インピーダンス

•

負荷RLから見た増幅回路の出力側の内部インピーダンスZout

•

等価回路で考えるとTrの出力インピーダンス1/hoeとコレクタ抵抗R2との並列回路が出力インピーダンスになる。

•

正確には、コンデンサC2のインピーダンス1/jwC2が直列に入ったものが出力インピーダンスになる。

周波数特性(f-特)p55-57

•

低域の減衰:カップリングコンデンサによる

•

高域の減衰:浮遊容量による

フィードバック

•

増幅回路の出力信号の一部または全部を入力に戻すことをフィードバック(feedとは食事を与えるという意味で昔は饋還と訳しましたが、現在では帰還と訳しています)といいます。

•

フィードバックされた信号が入力信号と同位相であれば正帰還、逆位相であれば負帰還といいます。

•

正帰還は発振回路として使われます。

•

負帰還は、回路のもつ最大の増幅率を犠牲にして、

(1)増幅度の安定、(2)ひずみ、雑音の低減、(3)周波数特性の改善、(4)入出力インピーダンスの調整などを図ります。

負帰還の原理 p64

•

V1=Vi-bV2, V2=A0V1

•

V2=A0 (Vi- bV2)より、(1+A0b)V2=A0Vi

•

全体の増幅率 A=V2/Vi=A0/(1+A0b)=1/(1/A0+b)

•

A0®\のとき A®1/ bとなり、

増幅率はA0に依存しなくなる。

負帰還による周波数特性(f特)の改善

•

負帰還をかけると、回路全体としての増幅度Aは1/(1/A0+b)=A0/(1+A0b) となり、もとの増幅率に比べ1/(1+A0b) に減少する。高域、低域ではA0 が落ちているので、分母(1+A0b) が小さくなり結果的に帯域幅が広くなる。

トランジスタの負帰還回路

•

コレクタ電位VCを帰還抵抗Rfを通してベースに帰還

•

エミッタ電流をエミッタ抵抗Rfを通じてVEとして帰還

エミッタ抵抗による負帰還

vi=hieib+(hfe+1)ibRE, vo=hfeibRL’

vo=-hfeibRL’={hfeRL’/(hie+(hfe+1)RE)}vi

A=vo/vi= hfeRL’/{hie+(hfe+1)RE}=140´5.97/(15+141´0.49)=9.94

見方を変えるとA0= hfeRL’/hie;

b=vf/vo=(hfe+1)RE/hfeRL’

A= A0/(1+A0b)

負帰還回路の入力インピーダンス

Zin=vi/ib={hieib+(hfe+1)RE ib}/ib=hie+(hfe+1)R

入力インピーダンスはhieにREのhfe倍が付け加わるので、かなり高くなる。

自己バイアス型帰還

if=i2+hfeib, v1=ibhie, v2=i2Rc, if=(v1-v2)/Rf

(v1-v2)/Rf=v2/Rc+(hfe/hie)v1

(1/Rf-hfe/hie)v1=(1/Rc+1/Rf)v2

A=v2/v1=(1/Rf-hfe/hie)/(1/Rc+1/Rf)

2段増幅器の負帰還

等価回路

A1=R6hie2hfe1/(R6+hie2)

(hie1+RE1(1+hfe1)

A2=hfe2RL’/hie2

b=Vo/Vf=RE1/(Rf+RE1)

実用エレクトロニクスコーナー

コンピュータ第2回

Z80計算機の構成

中京大学のホームページからhttp://www.ccad.sccs.chukyo-u.ac.jp/~mito/syllabi/circuit/z80/

1. Z80

Z80はインテル社の初期の製品である8080プロセッサを発展させ、ザイログ社が開発した、1チップcpuです。現在でも、組込み型CPUの基本的な命令体系となっている。

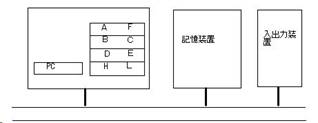

Z80は16ビットのアドレスバスと8ビットのデータバスを持ち、メモリや外部装置とのデータ交換を行う。Z80はCPU (Central Processing Unit)機能を有するのみで、記憶装置を持たないため、単体では動作させることができない。

2. Z80のシステム

a.

メモリ

Z80の外部にメモリや入出力装置をバスを通して接続すると、計算機として利用できるようになる。メモリには、不揮発型メモリ(ROM)と、揮発性メモリ(RAM)から構成される。Z80の外部にメモリや入出力装置をバスを通して接続することにより、計算機として利用できるようになる。

b.レジスタ

Z80は内部に複数のレジスタ(記憶回路)を持ち、このレジスタを利用して演算を行う。レジスタは、

A,B,C,D,E,H,L

で、各8ビットである。BC, DE, HLは結合して16ビットのアドレスを保持することができる。例えば、HLレジスタの番地のメモリを読みとり、その内容をAレジスタに読み出す命令がある。逆に、Aレジスタの内容を、HLレジスタの番地に書き込むことも出来る。

c.

演算とフラグレジスタ

演算はレジスタAが中心でこのレジスタに他のレジスタの値を加算、減算できる(乗算命令はない)。演算した結果は0、正、負、になるが、この結果はフラグレジスタに記録される。演算結果が0なると、「Z(zero:0)フラグが立つ」と言う。同様に、結果が負の場合、「S(sign:符号)フラグ」が立つ。

B.

プログラム例

1. 二つの番地の加算

Z80の8ビット加算命令を用いて二つのメモリの値を加算する。加算する番地を記号番地でDATA番地とDATA+1番地とする。加算結果はDATA+2番地に記憶する。レジスタHとLは対にして16ビットのHLのレジスタとして、メモリの番地を指示することが出来る。LD HL,DATA は HLレジスタの値をDATAの値に設定する命令で、LD A,(HL) はHLレジスタが指示するメモリの番地の内容をAレジスタに読み出す命令である。(HL)の括弧は"その番地のメモリの値"を意味する。

加算する一方の値はAレジスタであるから、まず、DATA番地の値をAレジスタに置き、これに次の番地の値を加える( ADD A,(HL) )。この前の INC HL 命令でHLの値は1増して、次の番地になっている。加算の結果はAレジスタに残るから、LD (HL),A で、AレジスタをDATA+2の番地に書き込む。これを記号プログラムで書くと次のようになる。

ORG

8000h プログラムの先頭番地

8000 21 09

80 LD HL,DATA HLをDATA番地にする

8003 7E LD

A,(HL) HL番地をAレジスタに読む

8004 23 INC

HL HLを増して101hとする

8005 86 ADD

A,(HL) 101h番地の内容を加える

8006 23 INC

HL HLを増して102hとする

8007 77 LD

(HL),A 結果を102hに記憶する

8008 76 HALT 停止

8009 0A DATA:DB

10 データ1

800A 14 DB

20 データ2

800B 00 DB

0 加算結果を記憶する

END

INCはIncrementの略で1だけ増すことを示す。メモリは連続した番地を利用しているので、直接番地を指定するより INC 命令を利用する方が簡単である。DBはDefine

Byteの略で、次の数値を1バイトの2進数に変換して保存することを示す疑似(宣言)命令である。

2. 乗算

Z80には乗算命令はないから、乗算するには乗算プログラムを作成する必要があります。a * b (b>0)の最も簡単な手法は、aをb回加えることである。被乗数aはDATA(8010h)番地、乗数はDATA+1番地にあり、結果はDATA+2(8012h)番地に保存するものとする。また、乗数は正とする。

プログラムでは、まず、LD B,(HL) でDATA番地の内容をレジスタBに、INC HL と LD

C,(HL) で次の番地の内容をレジスタCに転送し、LD

A,0hでレジスタAの値を0にする。

次に DEC C でレジスタCの内容を1づつ減らしながら、Cの値が0になるまで ADD A,B でレジスタBの値をAに加える。JP NZ,LOOP は直前の演算(DEC

C: Cを減らす)で結果が0でないとき LOOP の番地に"飛ぶ"ことを示す。JPはJumP、NZはNotZeroの略である。また、LOOP は記号番地で命令 ADD A,B の番地を示す。

これで、C(乗数)の回数だけ加算が行われるから、Aレジスタに b * c の値が残る。最後に A をメモリのDATA+2番地に保存する。

ORG 8000h

8000 21 10 80 LD

HL,DATA レジスタHLをDATA番地に設定

8003 46 LD

B,(HL) 被乗数をレジスタBに

8004 23 INC

HL

8005 4E LD

C,(HL) 乗数をレジスタCに

8006 3E 00 LD A,0h レジスタAを0にする

8008 80 LOOP:ADD

A,B レジスタBをAに加える

8009 0D DEC

C レジスタCを1減らす

800A C2 08 80 JP NZ,LOOP 0でなければLOOP番地へ飛ぶ

800D 23 INC

HL レジスタHLを増す

800E 77 LD

(HL),A 結果を記憶

800F 76 HALT 停止

8010 5 DATA:DB

5 被乗数

8011 10 DB

10 乗数

8012 0 DB

0 結果を保存する

END